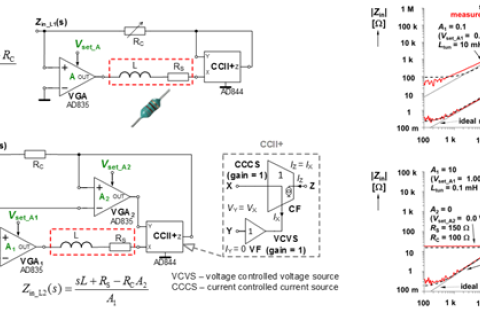

Pracovníci z Ústavu radioelektroniky a telekomunikaci představili novou metodiku elektronického ladění indukčnosti reálných cívek včetně eliminace sériových ztrát (v praxi desítek až stovek Ohmů). Současný stav neřeší problém skutečného sériového odporu miniaturizovaných cívek, což je prakticky nejdůležitější parazitní vlastnost v pásmech nízkých a středních frekvencí. V tomto případě není možné použití záporného odporu v sérii s cívkou (problémy se stabilitou). V práci jsou představena dvě řešení, umožňující nastavení a eliminaci sériového odporu a elektronické ladění/řízení hodnoty indukčnosti (pracovní rozsahy v rozmezí 0,1 až 1 mH a 0,1 až 10 mH). Navržené postupy byly experimentálně vyzkoušeny ve dvou aplikacích (elektronicky laditelný LC oscilátor a RLC filtr). Prezentovaná metodika nabízí zlepšení parametrů při návrhu obvodů využívajících cívky (problémy se sériovém odporem cívek, pokud jsou v procesu dostupné, jsou podstatné i v integrovaných obvodech).

Příslušný článek je dostupný na: